IEDM 2020: Intel wants to double their density through stacked transistors

Source: Hardware Luxx added 04th Jan 2021At this year’s IEEE International Electron Devices Meeting (IEDM), Intel presented various further and new developments in the field of manufacturing technologies. One of the most important researches concerns the so-called Self-Aligned 3D Stacked Multi-Ribbon CMOS transistors – self-aligning, stacked transistors, which should theoretically enable Intel to increase the transistor density

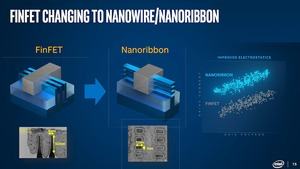

The transistors of modern semiconductor components are in the form of FinFET transistors a kind of 3D transistor, but they are still arranged in a planar design, i.e. side by side. Just like Samsung and TSMC, Intel is working on new types of transistors with nanosheets and nanoribbons or nanowires and uses them to manufacture gate-all-around transistors. GAA transistors are field effect transistors (FET) with gates wrapped around ultra-thin channels on all four sides. This improved gate control of the channel overcomes the physical scaling and performance limitations of FinFETs and allows for further scaling of the supply voltage. This improves the performance of the transistors.

In the future, Intel wants to halve the area occupied by such a transistor by using Self-Aligned 3D Stacked Multi-Ribbon CMOS transistors . For this purpose, two of the transistors are manufactured stacked, but not in a separate manufacturing step (in which, for example, they are manufactured separately from one another and then brought back together), but in a single step. To do this, however, adjustments must be made to the production of a nanosheet transistor.

In repeatedly repeating layers of silicon and silicon doped with germanium, a narrow fin is inserted, where the silicon-germanium is etched away, so that any number of nanosheets remains. The number of nanosheets can be used to control the voltage with which the transistor works and how much current can be passed through it.

At this point, Intel is introducing a further step: The The top two nanosheets are connected with phosphorus-doped silicon to form an NMOS component. The lower two are connected with boron doped silicon germanium to create a PMOS component.

According to Intel, the production of these processes is not a big problem. Nanosheet transistors are to be produced anyway. The division of the nanosheets should also be a solved problem. However, Intel now has to further optimize the performance of the two transistors, because splitting the nanosheet transistor compromises the performance of the two individual components.

It will take a few more years until Intel will mass-produce nanosheet transistors, or gate-all-around transistors in general. Most recently, Intel assumed at least five years. Samsung and TSMC are also working on similar technologies. The Self-Aligned 3D Stacked Multi-Ribbon CMOS transistors, however, offer completely different possibilities for Intel – especially with regard to the transistor density. Chips already consist of various types of transistors. This will continue in the future. ATM transistors can be particularly fast and represent an improvement of the current FinFET transistors. Self-aligned 3D stacked transistors enable a high packing density, for example in the caches and possibly SRAM. Intel’s future processors will most likely make use of this mixture of different transistor types.

Further innovations on the IEDM from Intel

In addition, Intel showed the first High-Performance Short-Channel Gate-All-Around transistors, the production of a GaN NMOS / Si CMOS integration on a 204 – mm wafer and demonstrated an integrated on-die metal -Interconnect system with air gaps and special geometries for the conductor tracks, in order to achieve an increase in the interconnect RC performance.

Sub-THz components on an organic substrate were also shown to be used for new vias processes.