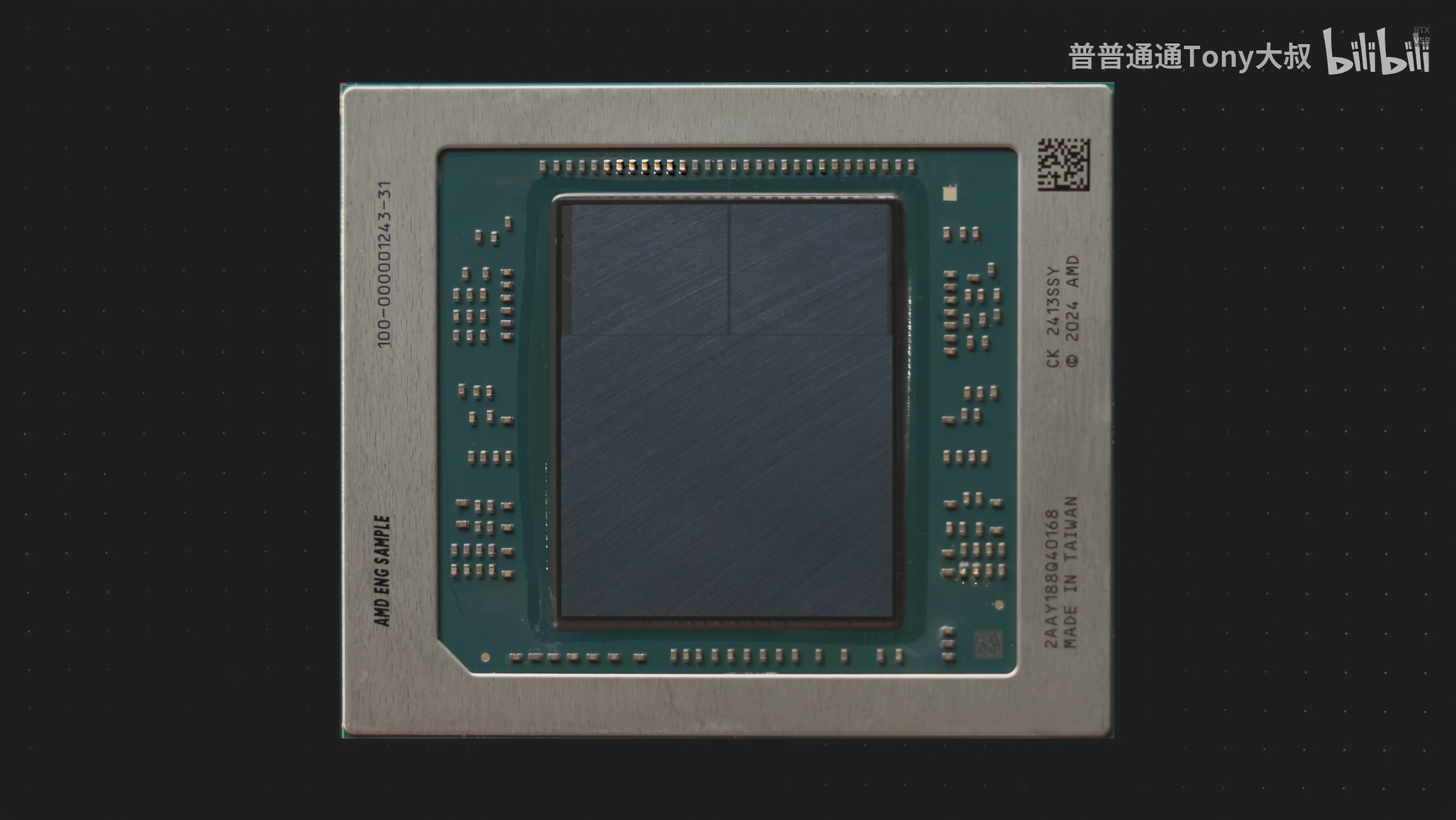

AMD’s Strix Halo reviews are no longer guarded by an embargo. So we’re seeing a wave of new die shots that underline the impressive engineering that went into the design of these chips. Thanks to Kurnal, Asus’ Tony Yu (at Bilibili), and Decap at X (formerly Twitter), we’re getting our first look at the internals of Strix Halo, formally known as Ryzen AI Max.

Let’s get one thing straight: Strix Halo isn’t your average run-of-the-mill APU. It wields 16 cores and 32 threads based on the latest Zen 5 architecture, alongside a massive 40 CU (Compute Unit) iGPU (integrated GPU). The package itself is composed of two Zen 5 CCDs, which are a tad different from the ones you see on Granite Ridge (Ryzen 9000 CPUs). Surrounding the chip are up to eight memory ICs, enabling support for 128GB of unified memory.

Thanks to high-res images from Tony Yu, we see that AMD has trimmed the D2D (Die to Die) interfaces between the CCD and I/O die by roughly 2mm. Although the CCDs have been tweaked slightly at 67.07mm2, they still support 3D V-Cache, evidenced by the TSV connections in the die shots. The rest is similar to what you’d typically find on a desktop Zen 5 processor. Each of the eight cores carries 8MB of dedicated L2 cache, with a shared 32MB L3 pool in between.

Beneath the two CCDs lies a large I/O die that hosts the uncore part of the chip. The bulk of the 307.58mm2 die size is occupied by the 40 Compute Unit integrated GPU (20 WGPs) developed using RDNA 3.5.

Slapping on more cores is only beneficial if they can be fed with data. We’ve seen firsthand how the performance of Strix Point (with 16 CUs) was hampered due to memory bottlenecks. AMD has taken a two-pronged solution to counteract this issue, with fast LPDDR5X memory across a wide 256-bit interface (eight 32-bit controllers) to the sides of the chip, and 32MB of MALL (Memory Access at Last Level) or LLC (Last Level Cache) split evenly across both sides of the iGPU.

To the left of the iGPU lies the XDNA 2 NPU (Neural Processing Unit), enabling 50 TOPS of AI performance, claimed to outclass even the RTX 4090. Some locations have been left unmarked. Either way, the bottom of the I/O die features a single PCIe 4.0 x16 interface, alongside USB 4 (40 Gbps), USB 3.2 Gen 2, and USB 2.0 controllers, followed by a Display Engine and two Media Engines with support for H.264, H.265, and AV1 codecs. Based on the provided statistics, the full chip equals roughly 441.72mm2 or allegedly 475mm2. That’s including what appears to be structural silicon.

The first laptops powered by Strix Halo should hit shelves later this month, with Asus’ ROG Flow Z13 tipped for a February 25 launch. While OEMs have initially been hesitant to jump on board with these chips, adoption is likely to improve, despite a slow initial uptake.