Earlier this year Taiwan Semiconductor Manufacturing Co. outlined plans to increase its CapEx budget to $25 billion ~ $28 billion in 2021, many industry observers attributed the increase to building out 3-nm capacities in preparation to produce CPUs for Intel and other large customers. This is not quite the case, according to a forecast by China Renaissance Securities.

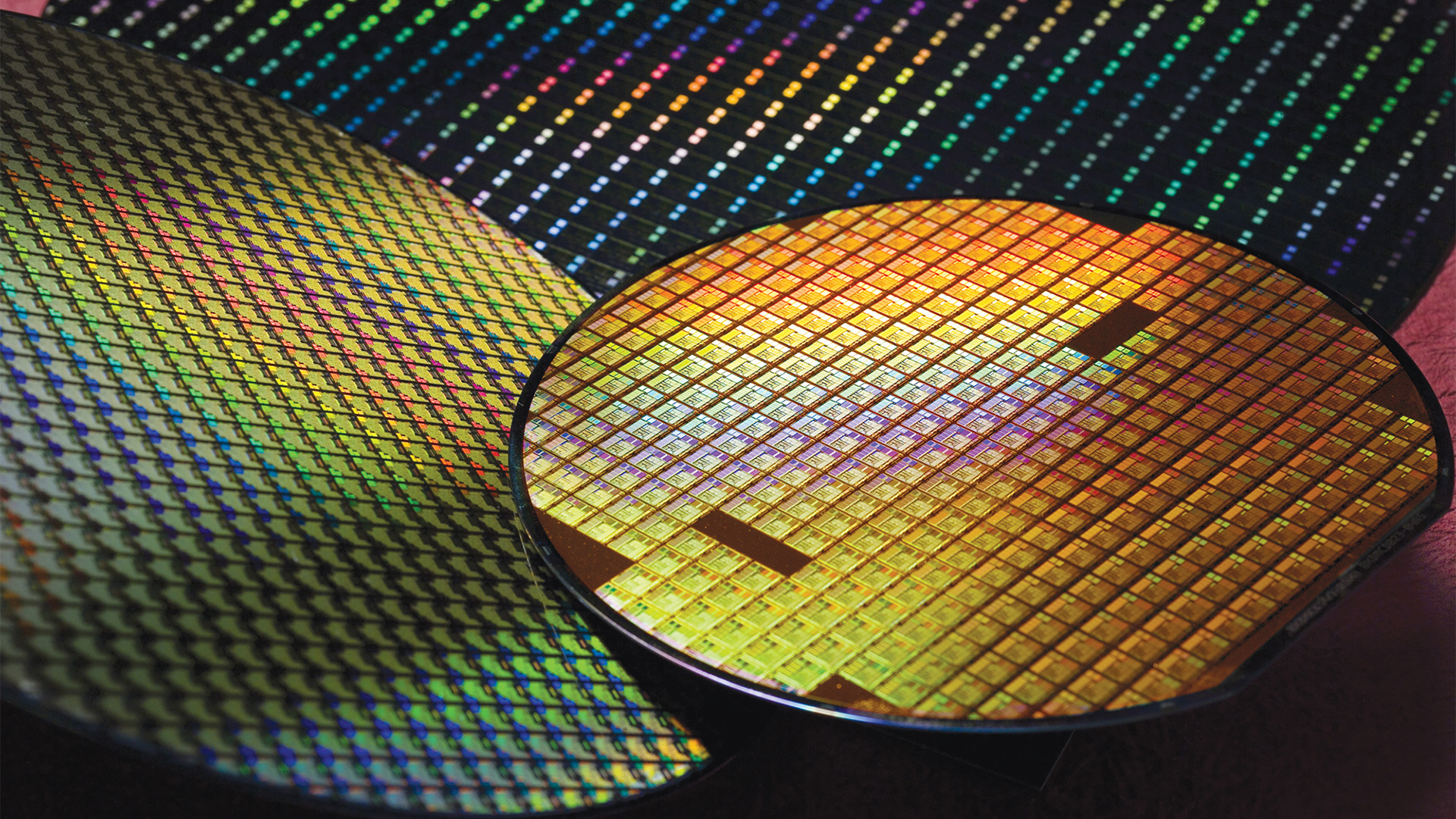

At present, TSMC’s N5 capacity is around 55,000 ~ 60,000 wafer starts per month (WSPM), according to a forecast by China Renaissance Securities, which reiterated it earlier this week. Given the fact that TSMC can no longer serve Huawei’s HiSilicon, the foundry’s main and biggest N5 customer is Apple, which uses this technology to produce its A14 Bionic as well as M1 system-on-chips for its latest products. Apple is one of TSMC’s key customers that has early access to the latest process technologies and is among the first to adopt the newest nodes.

Later this year other TSMC’s customers, such as AMD and Qualcomm, are projected to start using the manufacturer’s N5 fabrication process, which is when demand for this technology increases significantly. In a bid to satisfy demand for its N5 node in 2021 and in the following years, TSMC will spend the lion’s share of its CapEx on expansion of its N5 capacity, the analysts say.

China Renaissance believes that TSMC will increase its N5 capacity by two times compared to today’s levels, or to 110,000 ~ 120,000 WSPM, which essentially means that a year from now TSMC will have a GigaFab dedicated solely to N5 family, which includes N5, N5P, and N4 technologies. All of these processes are compatible on design rules, IPs, and SPICE levels, they will be used for years to come.

Another long node for TSMC will be its N3 (3 nm) technology. When compared to N5, the N3 process is expected to provide up to 15% performance improvement (at the same power and transistor count), or up to 30% power reduction (at the same speed and transistor count), along with up to 20% higher SRAM density and up to 70% higher logic density. TSMC expects N3 to enter risk production later this year, whereas volume production is expected in the second half of 2022. TSMC says that the interest towards N3 is higher than the interest towards N5 and N7 at the same stage of development (i.e., five to six quarters before formal launch).

Keeping in mind that N3 will not be needed for high volume manufacturing (HVM) for another year, it is logical for TSMC to spend big on N5 in calendar 2021 rather than prep for N3 in 2022 just now. The company is still expected to build a pilot N3 line with a capacity of around 10,000 ~ 15,000 WSPM this year.

Both N3 and N5 nodes extensively rely on extreme ultraviolet (EUV) lithography. To expand N5 capacities and equip an N3 fab, TSMC will need to procure loads of ASML’s Twinscan NXE scanners and deliver them. EUV tools take around six months to calibrate, so TSMC’s expansion plans have to be very precise in a bid get the equipment ready exactly when it needs them.

The main uncertainty for TSMC (and to a large degree the semiconductor industry) today is Intel’s outsourcing plan. So far, the company has disclosed plans to outsource certain GPUs and SoCs to TSMC and it is believed that these chips will be made using TSMC’s N5 or N7 nodes. Yet, it is unclear whether the chip giant intends to outsource production of its mainstream and performance CPUs to TSMC.

From transistor density point of view, Intel’s 10nm SuperFin fabrication process (~100 MT/mm2) is comparable to TSMC’s N7+ technology (~115 MT/mm2), but Intel’s own technology might still be a better fit for the company just now as its CPUs have been tailored for this node. Meanwhile, TSMC’s N5 has a significant advantage in terms of transistor density (~170 MT/mm2), which is something hard to ignore particularly when it comes to GPUs. When Intel is ready with its 7 nm technology (which is projected to double its existing transistor density) sometimes in 2023, it will still be behind TSMC’s N3 by two or three quarters, which means that it will make sense for Intel to outsource some of its products to TSMC, exactly what the new chief executive Patrick Gelsinger told several weeks ago. Meanwhile, from CapEx allocation point of view it makes more sense for Intel to outsource a substantial portion of its products to TSMC and save on fabs.

“In the interest of engineering resource/CapEx allocation, Intel would be unlikely to run a hybrid internal-external foundry production for the same process, in our view; thus we expect any outsourcing decision will be a binary outcome (i.e., “winner takes all”, others take nothing),” wrote Szeho Ng, an analyst with China Renaissance Securities, in a note to clients. “Given that TSMC has clearly been well ahead of Intel in terms of EUV tech and capacity readiness, we expect CPU outsourcing for Intel to be the best path forward considering its current stance.”

If Intel proceeds with the plan to outsource a significant portion of its production to TSMC in a bid to catch up with AMD in 2022, then it remains to be seen whether the foundry will have enough capacity to serve Intel and its existing customers, especially keeping in mind the fact that demand for N3 node may be higher when compared to demand for current nodes due to AI, HPC, and edge computing megatrends.

While it makes a great sense from financial point of view for Intel to CapEx save money and use TSMC’s manufacturing capacities to build its products while concentrating on architectural innovations, it may not be exactly a good plan for Intel’s long-term future. TSMC already has more EUV experience than Intel and it also has a certain standard-setting capability in the EUV ecosystem. If Intel does not catch up, then it will follow for many years to come and will not be able to use its superior fabrication processes as a competitive advantage over rivals.