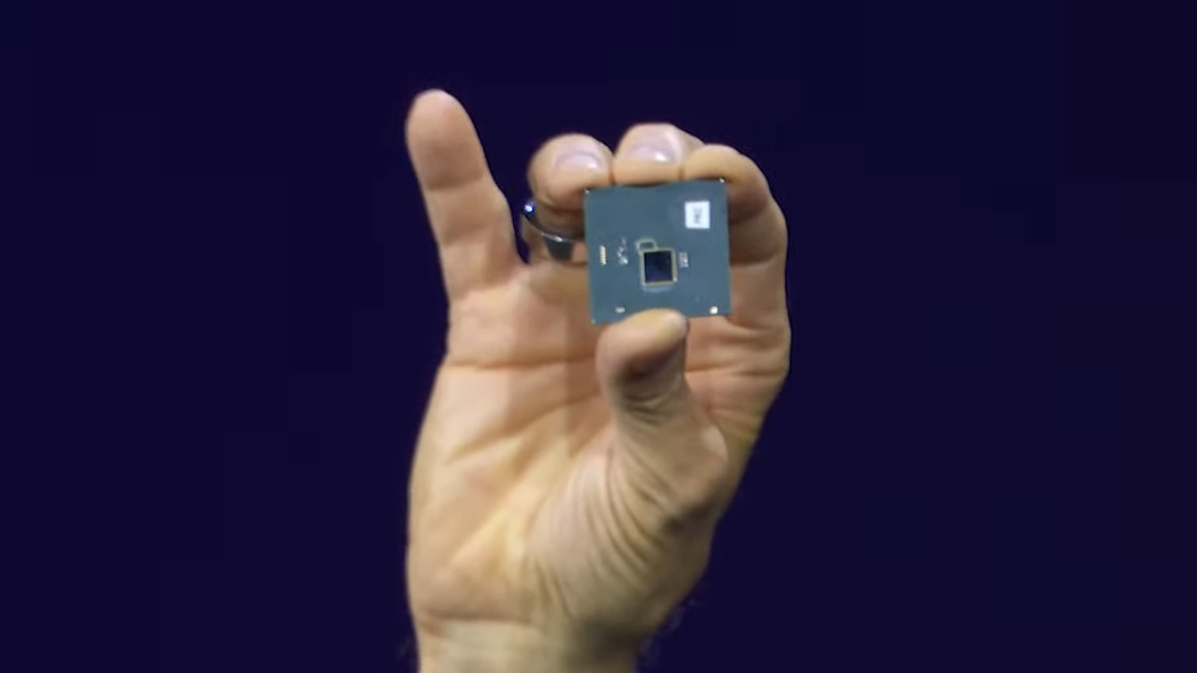

Intel CEO Pat Gelsinger displayed the world’s first UCIe-connected chiplet-based processor here at Innovation 2023, marking the first public display of working UCIe-enabled silicon. The chip features an Intel UCIe IP chiplet fabbed on its own Intel 3 process node paired with a Synopsys UCIe IP chip fabbed on the leading-edge TSMC N3E node. The two chiplets communicate via Intel’s EMIB interface.

The Universal Chiplet Interconnect Express (UCIe) interface is supported by a wide range of industry stalwarts, like Intel, AMD, Arm, Nvidia, TSMC, and Samsung, among 120 others. This interconnect is designed to standardize the die-to-die interconnects between chiplets with an open-source design, thus reducing costs and fostering a broader ecosystem of validated chiplets.

Today’s multi-chiplet packages use proprietary interfaces and protocols to communicate with one another, making broad adoption of third-party chiplets a daunting task. The goal of UCIe is to create an ecosystem with a standardized interface so one day chipmakers will be able to simply select chiplets from other designers and snap them into their new designs with a minimum of design and validation work.

The UCIe consortium was created last year, deep-dive details here, and it has already enjoyed broad support for the chipmaking industry. The spec debuted at version 1.0, but has now moved on to the 1.1 spec outlined in the album above. The consortium has outlined very aggressive performance and area targets, carving the target markets into two broad ranges, with standard 2D packaging techniques and more advanced 2.5D techniques (EMIB, CoWoS, etc.). Naturally, the advanced packaging options provide higher bandwidth and density.

Intel’s chiplet-based processors, like Sapphire Rapids and the newly announced Meteor Lake, currently use a proprietary interface and protocol for communication between the chiplets, but Intel has announced that it will use the UCIe interface after its next-gen Arrow Lake consumer processors. AMD and Nvidia are also working on their own initiatives, and you can read about those efforts in those links. Neither has shown working silicon.

We’re here at the show and will update with additional details about the test chip as they emerge.