Phison’s PS5018-E18 is a high-performance PCIe 4.0×4 NVMe SSD controller that has flooded the market in many of the newest and fastest-performing SSDs. It offers up very fast sequential performance but has been outshined in random responsiveness by top picks like Samsung’s 980 Pro and WD_Black SN850 due in part to Micron’s B27B 96-Layer TLC flash holding it back. Today, we’re taking a deep look at the company’s next iteration that gets a little help from Micron’s fastest flash yet.

While the first generation of E18-based NVMe SSDs used flash that interfaced with the controller flash at somewhat restricted speeds of 1,200 MTps, our second-gen sample is no longer shackled by this bottleneck. Now, featuring Micron’s latest B47R 176-layer TLC flash operating at speeds of up to 1,600 MTps, our new sample offers much more competitive performance. Still, this is only a preview, and while SSDs based on this flash due to hit the market soon, they will only hit the market after a few more firmware revisions.

Specifications

| Product | 500GB | 1TB | 2TB |

|---|---|---|---|

| Pricing | $99.99 | $159.99 | $319.99 |

| Capacity (User / Raw) | 500GB / 512GB | 1000GB / 1024GB | 2000GB / 2048GB |

| Form Factor | M.2 2280 | M.2 2280 | M.2 2280 |

| Interface / Protocol | PCIe 4.0 x4 / NVMe 1.4 | PCIe 4.0 x4 / NVMe 1.4 | PCIe 4.0 x4 / NVMe 1.4 |

| Controller | Phison PS5018-E18 | Phison PS5018-E18 | Phison PS5018-E18 |

| DRAM | DDR4 | DDR4 | DDR4 |

| Memory | Micron 176L TLC | Micron 176L TLC | Micron 176L TLC |

| Sequential Read | 6,500 MBps | 7,000 MBps | 7,000 MBps |

| Sequential Write | 2,850 MBps | 5,500 MBps | 6,850 MBps |

| Random Read | 170,000 IOPS | 350,000 IOPS | 650,000 IOPS |

| Random Write | 600,000 IOPS | 700,000 IOPS | 700,000 IOPS |

| Security | AES 256-bit encryption | AES 256-bit encryption | AES 256-bit encryption |

Phison’s PS5018-E18 supports both TLC and QLC flash and can address capacities of up to 8TB, but most retail products will ship in the popular 1TB and 2TB capacities. In terms of performance specifications, Phison’s E18 hasn’t changed much besides the faster 1,600 MTps flash transfer rate. Sequential speeds are rated for up to 7.4/7.0 GBps read/write and in terms of random performance, and the company claims the SSD controller is capable of 1 million random read/write IOPS, given the proper flash and tuning.

Phison seems to be moving away from full dynamic SLC caching in the traditional sense. Instead, its SLC caching algorithms are adapting to better suit not only consumer workloads but heavy prosumer workloads, too. We will cover this more in-depth later in the article.

Phison didn’t reveal anything about end-product endurance ratings with this new flash, but it may help improve endurance ratings over current-gen devices. The Phison E18 still features the company’s fourth-generation LDPC ECC and RAID ECC along with a DDR ECC engine and end-to-end data path protection to ensure your data is programmed and read reliably over the product’s useful lifespan. It also supports various security options such as Pyrite, AES 256, SHA 512, RSA 4096, and TCG Opal. Additionally, it comes with S.M.A.R.T. data reporting and Trim support and secure erase and crypto erase capability.

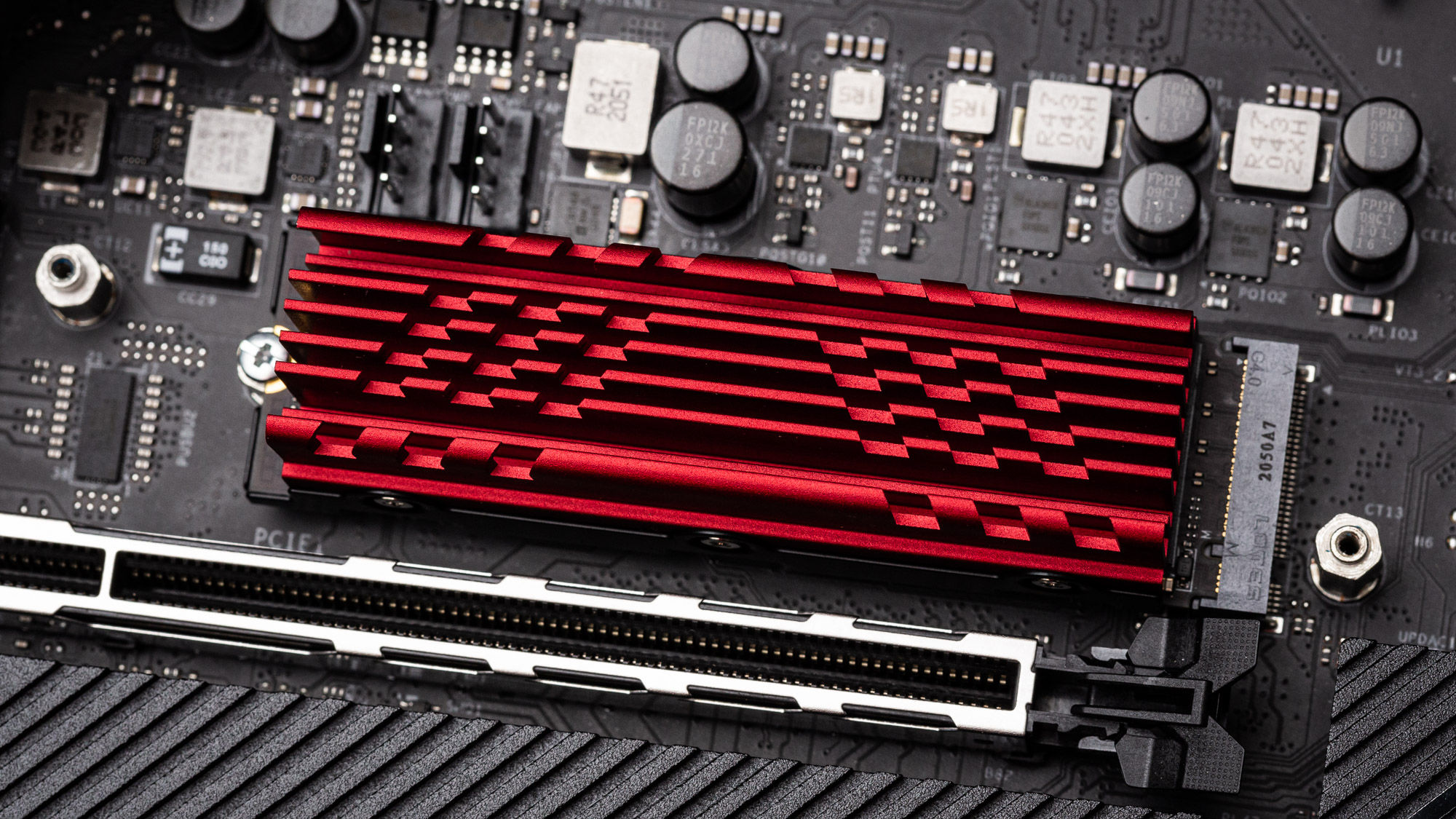

A Closer Look

The E18 interfaces with the host over a PCIe 4.0 x4 link and is NVM 1.4 compliant. Our 2TB sample comes in an M.2 2280 double-sided form factor, but smaller capacities come in single-sided form factors for broad compatibility with the latest ultra-thin mobile devices. This is in contrast to Samsung and WD M.2 SSDs, all of which come only in single-sided form factors.

Image 1 of 4

Image 2 of 4

Image 3 of 4

Image 4 of 4

The PS5018-E18 controller is an eight-channel, DRAM-based design. Our 2TB sample features two 1GB SK hynix DDR4 ICs, one on each side of the PCB. It leverages a Penta-core design with three single-core Cortex R5 CPUs handling the host/read/write tasks while an additional R5 CPU, in a lower-clocked dual-core configuration, acts as a co-processor. The E18’s primary cores are clocked much higher than the older E16’s cores, at 1 GHz versus 733 MHz.

The E18 comes with CoXPorcessor 2.0 technology, which offloads some of the firmware code from the primary cores to the dual-core R5 to ensure responsive QoS when hammered with heavy sustained workloads and aid power efficiency. One of the co-processor cores optimizes NAND die-queues to the flash while the other is for managing the DRAM/NAND tables.

Image 1 of 2

Image 2 of 2

The controller is manufactured on TSMC’s 12nm process technology and comes with multiple features to keep thermals under control while operating at high speeds. It features ASPM and ASPT support, can transition into the L1.2 low power state to sip just 3mW at idle, and can thermal throttle to preserve data integrity over performance.

Phison sent over our sample with a sleek-looking heat sink, but this heat sink does not necessarily indicate that retail models will require heat sinks to keep them cool under most consumer workloads. Although, when this controller is paired with 2TB of flash, it can gulp down over 8 watts of power under sustained load, which can create quite a bit of heat.

Speaking of the flash, our 2TB sample comes with thirty-two 512 Gb dies of Micron’s new B47R 176L TLC, aligning with the controller’s native chip enable capability to optimize interleaving, and thus, performance. Micron’s 176L TLC offers a significant improvement over previous generations, and not just due to its high layer count.

This flash features the company’s new replacement-gate architecture that combines charge traps with CMOS-under array (CuA) technology, allowing for roughly a 30% smaller die size than its competitors. Enabled through multiple advancements in the new architecture and firmware support, operating interface speeds clock in at 1,600 MTps, which improves read and write speed by roughly 35% compared to the company’s previous-generation floating-gate 96L TLC.

Image 1 of 3

Image 2 of 3

Image 3 of 3

Architecturally, Micron replaced the polysilicon control gates with metal, and it uses a different etching method compared to traditional NAND. This reduces resistance, thus allowing the program pulse to ramp up quickly, reducing programming complexities and overhead. The design reduces the electric field duration on the circuits since they can be programmed much more quickly. Micron also increased the etch diameter, allowing for more structural stability as the company ramps layer counts in future generations of the flash.

Additionally, in traditional NAND, cell-to-cell capacitive coupling issues limit performance, but by utilizing a nonconductive layer of silicon nitride (SiN) acting as a NAND storage cell, the replacement-gate design demonstrates almost no capacitance between cells.

These changes, along with other cell geometry adjustments, directly improve performance, endurance, conserve energy, and allow for increased storage capacity, especially as Micron continues to develop newer iterations of its flash.

MORE: Best SSDs

MORE: How We Test HDDs And SSDs

MORE: All SSD Content