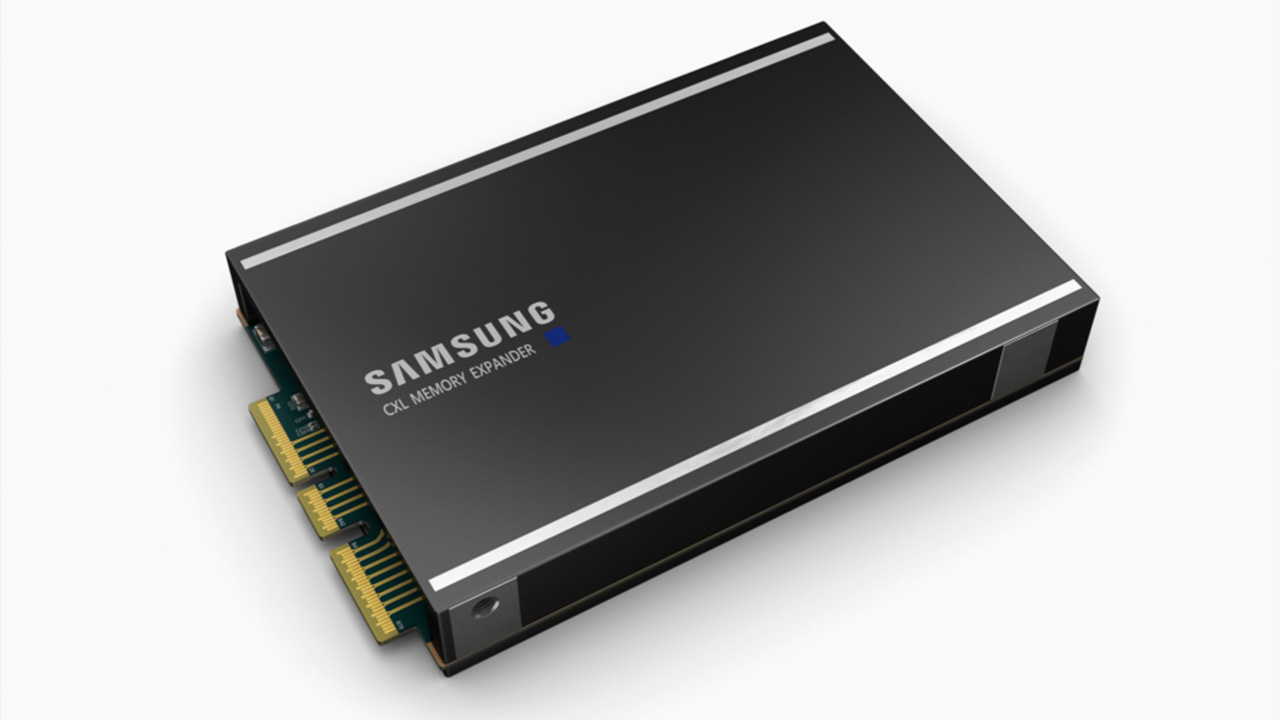

In a press release today, Samsung has announced memory modules based on the CXL standard, bringing together PCIe 5.0 and DDR5 for AI and high-performance computing work in data centers.

CXL is an open standard first mooted in 2019, with a view to bringing high-speed, low latency communication between a CPU and its RAM, accelerator cards, and other devices, while expanding memory capacity and bandwidth greatly. CXL is based upon the industry supported PCIe 5.0 interface. With the new standard, which removes the limitations of limited memory channels, Samsung foresees RAM capacity scaling to multiple terabytes.

The Compute Express Link Consortium includes Samsung, AMD, ARM, IBM, Intel, Broadcom, Micron, and Nvidia among many others. It has previously been seen in Agilex FPGAs (Field Programmable Gate Arrays) made by Intel via its purchase of Altera Corporation.

It’s not just the new standard that marks these new memory modules out. Samsung has added new controller technologies such as memory mapping, interface converting and error management to the mix, and the new module has been successfully validated on next-generation server platforms from Intel.

Dr Debendra Das Sharma, an Intel Fellow and Director of I/O Technology and Standards at Intel, said, “Data center architecture is rapidly evolving to support the growing demand and workloads for AI and ML, and CXL memory is expected to expand the use of memory to a new level. We continue to work with industry companies such as Samsung to develop a robust memory ecosystem around CXL.”